Difference between revisions of "Spiderboard SoM"

From spiderboard.org

| Line 20: | Line 20: | ||

:::::[[File:SpiderSoM-BD.png|500px]] | :::::[[File:SpiderSoM-BD.png|500px]] | ||

| + | |||

| + | == Downloads == | ||

The following components are available for download: | The following components are available for download: | ||

Revision as of 15:34, 12 April 2018

About SpiderSoM

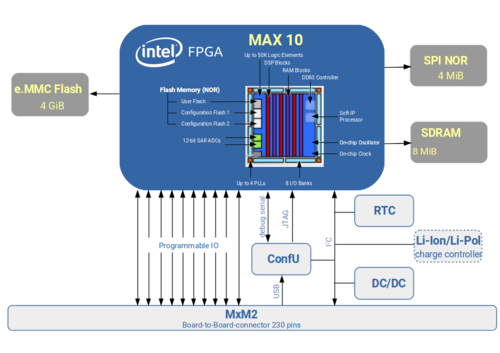

The SpiderSoM is a programmable, non-volatile solution based on Intel® MAX®10 FPGA, which enables it to deliver full-featured FPGA capabilities: support for various soft-core CPUs, video-processing algorithms, etc. The SpiderSoM promotes the free and open design concept: KiCAD design files are available under CERN OHL v1.2.

This module can be considered as a cost-optimized alternative to the MX10 module[1].

Featureset

- MAX 10 FPGA in F256 package

- module supports wide range of the devices: from 10M04DC to 10M50DA

- optional 4 MByte SPI NOR

- optional 4 GByte e.MMC

- optional 128/256/512MByte DDR3 DRAM (for 10M 16/25/40/50 FPGAs)

- programmable clock generator and PLL, with optional external reference input

- 178 FPGA GPIO pins, including 13 LVDS transmitters and 54 receivers

- RTC with battery backup

- programmable high-efficient PMIC, FPGA IO voltages are configurable

- optional Li-Ion/Li-Pol charger

- Size: 70mm x 35mm

Block Diagram

Downloads

The following components are available for download: