Difference between revisions of "RISC-V & FreeRTOS"

From spiderboard.org

| Line 26: | Line 26: | ||

== Compiling Firmware == | == Compiling Firmware == | ||

| − | + | ||

* Download the [ftp://ftp.aries-embedded.de/products/MX10/software/demo/20190506_SpiderSoM_quartus_riscv_freertos.zip RISC-V & FreeRTOS Example] and unpack. | * Download the [ftp://ftp.aries-embedded.de/products/MX10/software/demo/20190506_SpiderSoM_quartus_riscv_freertos.zip RISC-V & FreeRTOS Example] and unpack. | ||

| Line 41: | Line 41: | ||

* Copy the ''bootrom.mif'' to ''riscv_freertos_example/quartus'' | * Copy the ''bootrom.mif'' to ''riscv_freertos_example/quartus'' | ||

*: '''$''' cp out/bootrom.mif ../quartus | *: '''$''' cp out/bootrom.mif ../quartus | ||

| + | |||

| + | [[File:terminal_make_riscv.png|1200px|Terminal after calling make.]] | ||

== Quartus Prime Project == | == Quartus Prime Project == | ||

| Line 56: | Line 58: | ||

[[File:qsys-ram-init.png|900px|Setting the memory initialization in Qsys Platform Designer]] | [[File:qsys-ram-init.png|900px|Setting the memory initialization in Qsys Platform Designer]] | ||

* Compile the project and program it onto the FPGA using either [[Getting Started: Quartus Prime & OpenOCD#Programming via OpenOCD | OpenOCD]] or [[Getting Started: Quartus Prime & OpenOCD#Programming via USB Blaster| USB-Blaster]]. | * Compile the project and program it onto the FPGA using either [[Getting Started: Quartus Prime & OpenOCD#Programming via OpenOCD | OpenOCD]] or [[Getting Started: Quartus Prime & OpenOCD#Programming via USB Blaster| USB-Blaster]]. | ||

| + | |||

After programming: | After programming: | ||

| − | |||

| − | |||

* If the red LED on the module starts blinking once per second, the FPGA was programmed successfully. | * If the red LED on the module starts blinking once per second, the FPGA was programmed successfully. | ||

| Line 67: | Line 68: | ||

*: '''$''' sudo picocom -b 115200 /dev/ttyACM0 | *: '''$''' sudo picocom -b 115200 /dev/ttyACM0 | ||

** Every character written is looped back and should be displayed on the terminal. | ** Every character written is looped back and should be displayed on the terminal. | ||

| + | |||

| + | [[File:terminal_picocom.png|500px|Characters written are looped back and displayed.]] | ||

== Downloads == | == Downloads == | ||

Revision as of 12:43, 27 May 2019

Contents

Prerequisites

- Linux Operating System (this guide uses Ubuntu 16.04)

- Utility Software (git, make)

- Quartus Prime

- A SpiderSoM (alternatively MX10) with SpiderBase

- One of the following:

- OpenOCD

- USB Blaster and Quartus Programmer

Installing VectorBlox ORCA Core and RISC-V Tools

- Download the source from https://github.com/VectorBlox/orca using git.

- This guide uses the install locations /opt/orca/ and /opt/riscv/, you can substitute them if you wish.

- Open a terminal window and run:

- $ git clone https://github.com/VectorBlox/orca.git /opt/orca

- $ cd /opt/orca/tools/riscv-toolchain/

- $ export RISCV_INSTALL="/opt/riscv"

- $ ./build-toolchain.sh

- Info: This may take a while.

- Finally, add the RISC-V tools to your path. Open .profile in your home directory with a text exitor and add the line:

- PATH="/opt/riscv/bin:$PATH"

- After updating the path variable you may need to logout and login again or run the following command in the terminal:

- $ source ~/.profile

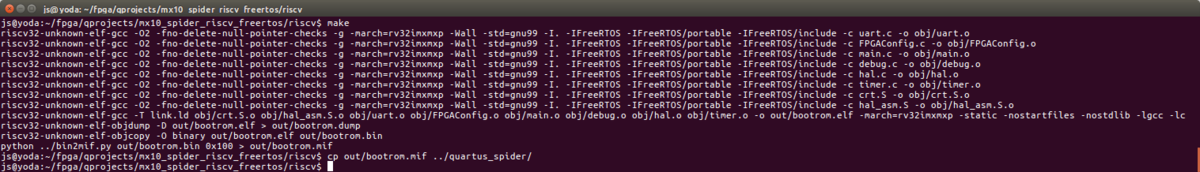

Compiling Firmware

- Download the RISC-V & FreeRTOS Example and unpack.

- Then choose either RISC-V or RISC-V & FreeRTOS and run make.

- For this, open a terminal window and run the commands:

- $ wget ftp://ftp.aries-embedded.de/products/MX10/software/demo/20190506_SpiderSoM_quartus_riscv_freertos.zip

- $ unzip 20190506_SpiderSoM_quartus_riscv_freertos.zip

- For the RISC-V standalone demo:

- $ cd riscv_freertos_example/riscv

- Or for RISC-V with FreeRTOS:

- $ cd riscv_freertos_example/riscv_freertos

- $ make

- This will create the bootrom.mif (Memory Initialization File) in the subfolder out.

- Copy the bootrom.mif to riscv_freertos_example/quartus

- $ cp out/bootrom.mif ../quartus

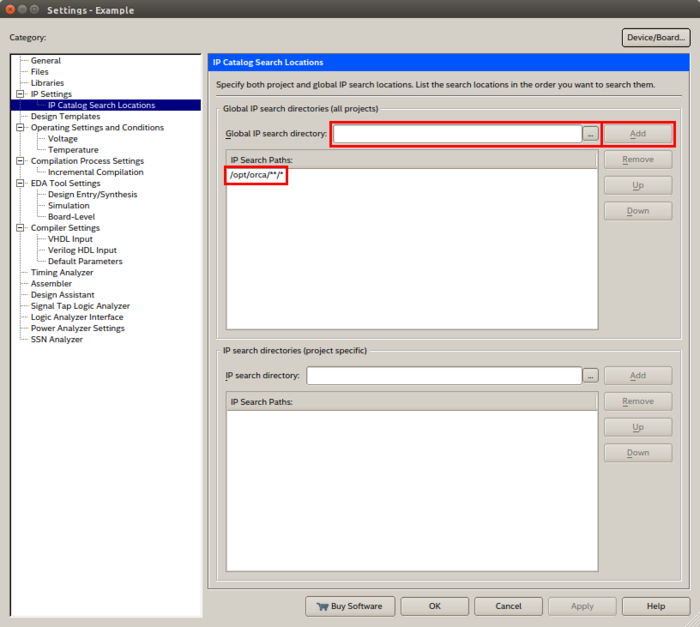

Quartus Prime Project

- Open Quartus Prime and load the project under riscv_freertos_example/quartus.

- INFO: This Quartus project is specific to the SpiderSoM - for the MX10 the pin assignment has to be changed.

- Open Assignments -> Settings -> IP Settings -> IP Catalog Search Locations and add the search path to ORCA.

- If ORCA was installed under /opt/orca/ then type in as search path /opt/orca/**/* and click on the Add button.

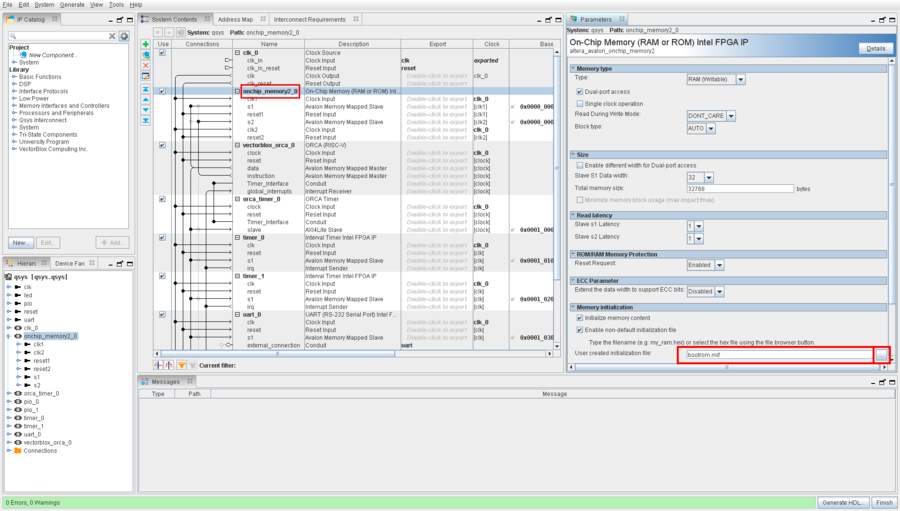

- (Optional) Launch Qsys Platform Designer and open qsys.qsys

- (Optional) Under System Contents, double-click onchip_memory2_0 and under memory initialization provide your bootrom.mif file. Per default the bootrom.mif in the quartus folder will be used.

- (Optional) Save and Generate the Qsys system.

- Compile the project and program it onto the FPGA using either OpenOCD or USB-Blaster.

After programming:

- If the red LED on the module starts blinking once per second, the FPGA was programmed successfully.

- If the green LED on the module starts blinking once every two seconds, the RISC-V Core and its firmware is working.

- PMod J2 will output a binary counter.

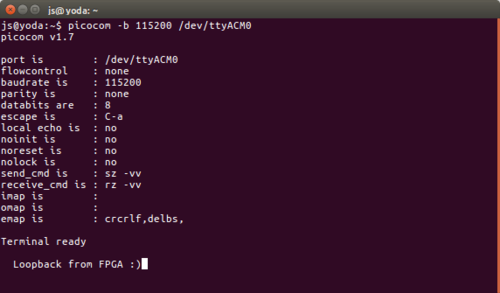

- You can use the UART of the FPGA by using standard tools such as picocom:

- $ sudo picocom -b 115200 /dev/ttyACM0

- Every character written is looped back and should be displayed on the terminal.